Published by: BhumiRaj Timalsina

Published date: 30 Jun 2021

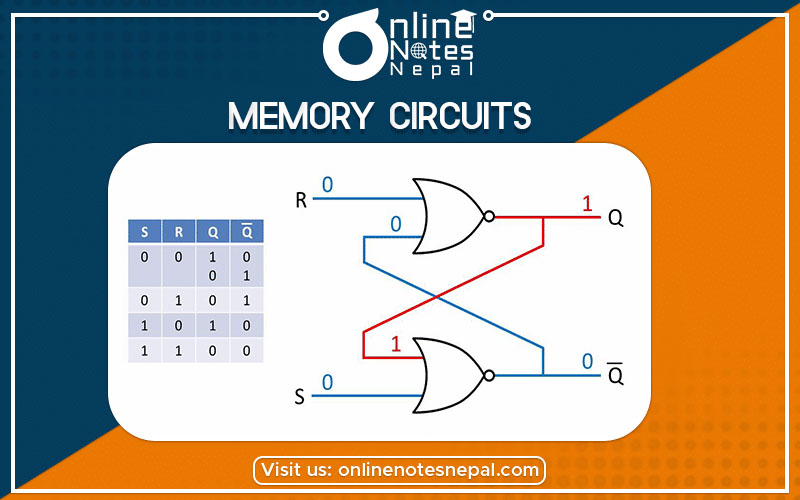

The electronic circuits whose output remains as set until something is done to change are called memory circuits. Logic circuits that incorporate memory cells are called sequential logic circuits.

The memory elements used in clocked sequential circuits are called flip-flops. These circuits are binary cells capable of storing one bit of information. A flip-flop circuit has two outputs, one for the normal value and one for the complement value of the bit stored in it.

Flip Flops are of different types depending on how their inputs and clock pulses cause a transition between two states. They are:

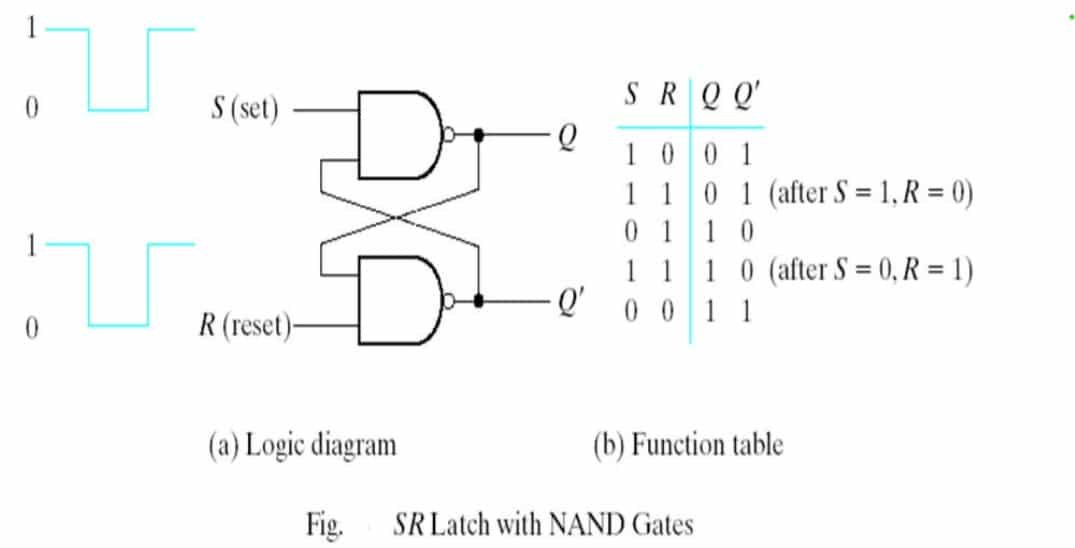

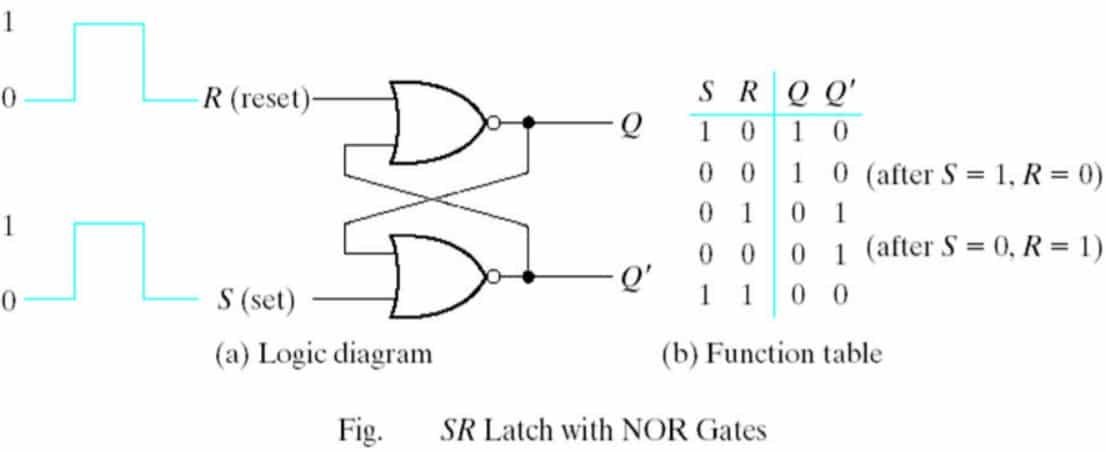

The SR latch is a circuit with two cross-coupled NOR gates or two crosscoupled NAND gates. Each flip-flop has two outputs, Q and Q’, and two inputs, set and reset. The cross-coupled connection from the output of one gate to the input of the other gate constitutes a feedback path. For this reason, the circuits are classified as asynchronous sequential circuits.

A flip-flop has two useful states.

RS flip-flop with NOR gate

RS flip-flop with NAND gate