Published by: Nuru

Published date: 22 Jun 2021

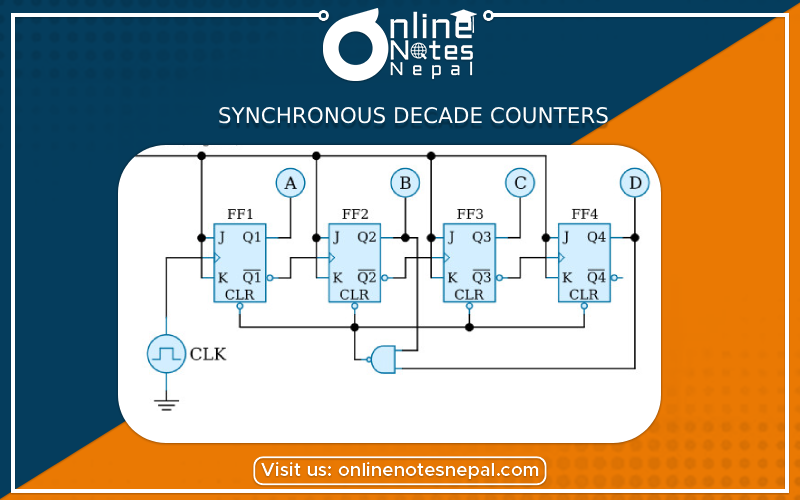

Synchronous Decade Counters are that counter that counts from 0 to 9 and recycles to 0 again. This is done by forcing the 1010 state back to the 0000 states. Because of the return of 0 after a count of 9, the BCD i.e. Binary Coded Decimal Counter does not have a regular pattern as the straight binary counters have in them.

The following decade counter can be drawn using the J K flip-flop. The figure is given below:

pic

Fig: A Synchronous Decade Counter

pic

Fig: Timing Sequence of a Decade Counter

The timing sequence of the decade counter is shown above. From the above-given sequence, we can see that there is an occurrence of toggle in each of the outputs. Q 0 toggles on each clock pulse above. Likewise, Q 1 toggles in the clock pulse each time when Q 0 =1 and Q 3 = 0. Following this, Q 2 changes on the next clock pulse again each time when Q 0= Q 1 = 1. Then, Q 3 changes on the next clock pulse each time Q 0 = 1 and Q 2 = 1 (which happens in the count 7), or then Q 0 = 1 and Q 3 = 1 ( which happens in the count 9 ).

The second flip-flop changes on the next clock pulse each time both the Q 0 = 1 and Q 1 = 1. Thus, both the inputs of the second flip-flop, i.e. J = K = Q0 Q1.

The third flip-flop in the circuit changes to the opposite state on the next clock pulse each time when Q 0 = 1, Q 1 = 1, Q 2 = 1 in the stage 7 or in the state 9 by Q 0 = 1 and Q 3 = 1.

Thus it becomes, J = K = Q0Q1Q2 + Q0Q3.