Published by: Nuru

Published date: 22 Jun 2021

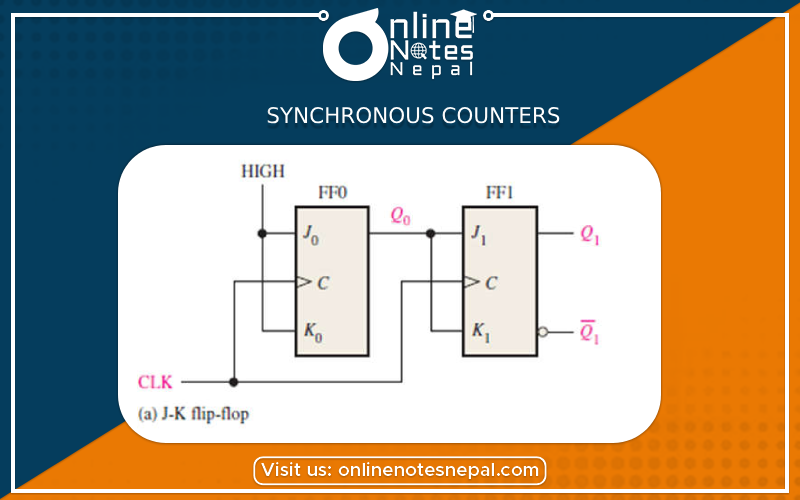

Synchronous Counters are those counters which count the number of events in the circuit that takes place in the same interval of time every time it works. In these types of counters, the clock inputs of all flip-flops are connected together and are triggered by the input pulses. Synchronous counters are distinguished from ripple counters in that clock pulses are applied to the CP i.e. clock pulse inputs of all flip-flops. The common pulse triggers all the flip-flops simultaneously, rather than one at a time in succession as in a ripple counter. The decision of whether a flip-flop is to be complemented or not is determined from the values of the J and K inputs at the time of the pulse if we are using the J K flip-flop.

It has two flip-flops in its design. And it gets triggered in some intervals of time. The following given diagram is a 2-Bit Binary Counter.

We should notice what happens after the 2nd clock pulse. Both the outputs i.e. of the first and that of the second are high. The positive edge of the 3rd clock pulse will cause both the flip-flops of the counter to reset.

pic

Given below is the circuit of the 3-Bit Binary Counter. Initially, the J and K inputs of the first flip-flop are connected to high. The second flip-flop’s J and K inputs are connected to the output of the first flip-flop. Following this, the J and K inputs of the third flip-flop are connected to the output of the AND gate. This AND gate is fed by the outputs of the first and the second flip-flops.

pic

After the third clock pulse, a phenomenon should be noticed. Both the outputs i.e. of the first and the second flip-flop are at high. Here also, the 4th clock pulse causes the third flip-flop to change its state. This is due to the AND gate.

Below given is the circuit diagram of the 3-Bit Binary Counter.

The timing diagram is given below:

pic

One of the most important advantages of synchronous counters is that there is no cumulative delay because all the flip-flops are triggered in a parallel way. So, the maximum operating frequency for the counter will be higher than for the corresponding ripple counter.

Below given is the figure of the 4-Bit binary counter.

pic

We can see that the external clock pulses are fed directly to each of the flip-flops in the counter chain. Both the J and K inputs are tied in a toggle mode but only in the first flip-flop, they are connected to the logic ‘1’ i.e. high. This allows the flip-flop to toggle on every clock pulse.

The J and K flip-flips of the second flip-flop are connected directly to the output of the first flip-flop. But the J and K inputs of the third and fourth flip-flops are taken from the separate AND gates. These are also supplied with the signals from the input and output of the previous stages. These AND gates generate the required logic for the input of flip-flops of the next stage.

If we enable each flip-flop to toggle based on whether the outputs of each flip-flop are high, we can obtain the same counting sequence with the asynchronous circuit but without the ripple effect.

pic