Published by: Nuru

Published date: 22 Jun 2021

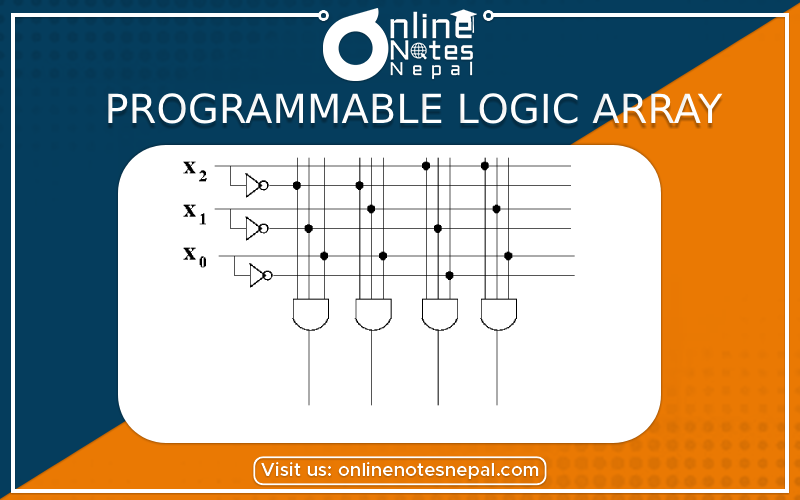

Programmable Logic Array is similar to ROM but doesn't provide full decoding of the variables and doesn't generate all the minterms as the ROM. The decoder of ROM is replaced by a group of AND gates, each of which can be programmed to generate a product term of the input variables. The AND and OR gates inside the PLA are initially fabricated with fuses among them. The specific Boolean functions are implemented in the sum of products form by blowing appropriate fuses and leaving the desired connections.

A block diagram of the PLA is shown in Fig. below. It consists of n inputs, m outputs, k product terms, and m sum terms. The product terms constitute a group of k AND gates and the sum terms constitute a group of m OR gates. Fuses are inserted between all n inputs and their complement values to each of the AND gates. Fuses are also provided between the outputs of the AND gates and the inputs of the OR gates. Another set of fuses in the output inverters allows the output function to be generated either in the AND-OR form or in the AND-OR-INVERT form. With the inverter fuse in place, the inverter is bypassed, giving an AND-OR implementation. With the fuse blown, the inverter becomes part of the circuit and the function is implemented in the AND-OR-INVERT form.

pic

The use of a PLA must be considered for combinational circuits that have a large number of inputs and outputs. It is superior to a ROM for circuits that have a large number of don't-care conditions. Let me explain the example to demonstrate how PLA is programmed.

Consider a truth table of the combinational circuit:

pic

pic

Programming the PLA means, we specify the paths in its AND-OR-NOT pattern. A typical PLA program table consists of three columns.

pic

Note:

There are three distinct product terms in this combinational circuit: AB', AC and BC. The circuit has three inputs and two outputs; so the PLA can be drawn to implement this combinational circuit.

pic