Published by: Nuru

Published date: 22 Jun 2021

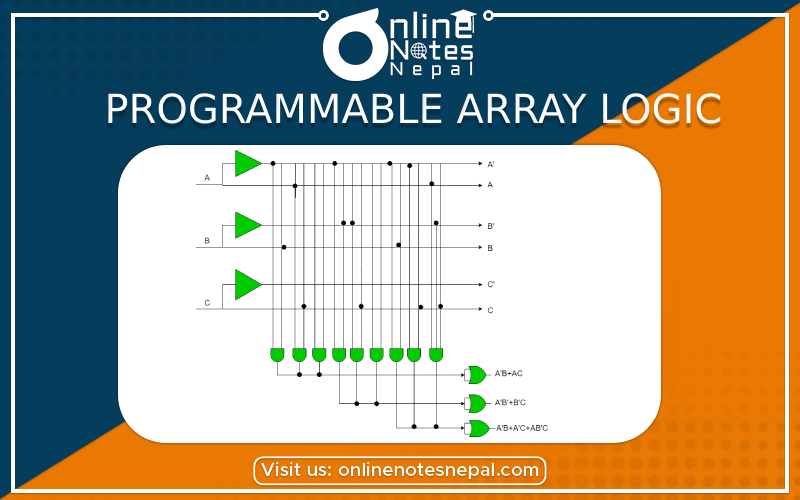

Programmable Array Logic (PAL) is a commonly used programmable logic device (PLD). It has a programmable AND array and a fixed OR array. Because only the AND array is programmable, it is easier to use but not flexible as compared to Programmable Logic Array (PLA). PAL’s only limitation is the number of AND gates.

PAL consists of small programmable read-only memory (PROM) and additional output logic used to implement a particular desired logic function with limited components.

The main difference between PLA, PAL, and ROM is their basic structure. In PLA, programmable AND gate is followed by a programmable OR gate. In PAL, programmable AND gate is followed by a fixed OR gate. Similarly, in ROM, fixed AND gate array is followed by programmable OR gate array.

Describing the PAL structure (programmable AND gate followed by a fixed OR gate).

Example: Realize the given function by using PAL:

Any form from the sum of product (SOP) form or product of sum (POS) can be used for the realization of a boolean function.

There are three inputs A, B, C, and three functions X, Y, Z. Using the sum of product (SOP) terms to express the given function as follows:-

Following the Truth table will be helpful in understanding the function of the number of inputs:

pic

Finding X, Y, Z:

Look for high minterms (function value is equal to 1 in the case of SOP) in each function output:

X = A’B + AC

Y = A’B + B’C

Z = A’B + A’C + AB’C

pic

AND array has been programmed but has to work with fixed OR array as per requirement. Desired lines will be connected to PLDs.