Published by: Nuru

Published date: 22 Jun 2021

Asynchronous Up-Down Counters are those counters which are able to count both up and down depending upon the status of control signals. Some count up from zero and provide a change in the state of output upon reaching a predetermined value; others count down from a preset value to zero to provide an output state change.

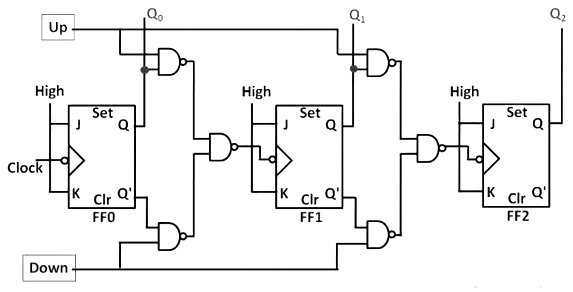

It has multiple numbers of counter blocks. Each of the counter blocks has a counter output, an up-down control output, and an up-down control input. A counter signal output from each of the counter blocks has at least two bits.

When the Up input is 1, then the Down input is 0. In this instance, the NAND network between the first flip-flop and second flip-flop will gate the Q output of the first flip-flop into the input of the second one. Likewise, the Q output of the second flip-flop will be gated through the next NAND network into the clock input of the third. This will result in the count up.

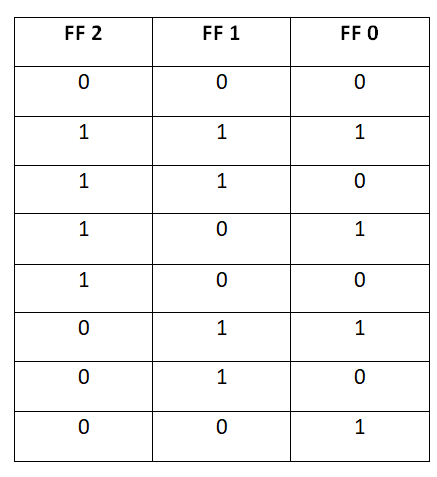

Opposite of the first process for the up count, there is the process for the down count. When the control input Up is at 0, then the DOWN one is at 1, the inverted outputs of the first and second flip-flops are gated into the clock inputs of second and third respectively. If the flip-flops are at 0, then the counter will go through the below-given sequence.

We notice in the whole operation that the up-down counter is slower than the up counter or a down counter. This is because of the addition to the propagation delay due to NAND circuits.

The difference in the up and down counter is that regarding the connection of the display ports. In Up counters, it is connected to the non-inverted output Q, and that in Down counters; they are connected to the non-inverted output n Q.