Published by: Dikshya

Published date: 13 Jul 2023

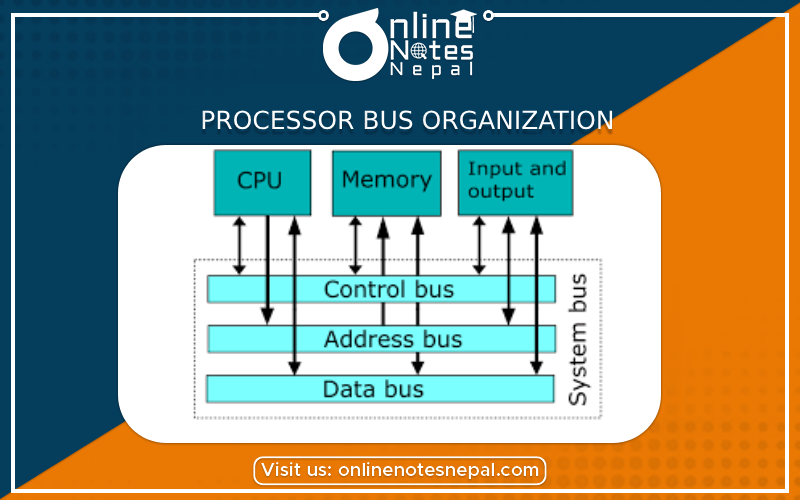

Processor bus organization refers to the structure and architecture of the bus system used in a computer processor. The bus system provides communication pathways for data, instructions, and control signals between various components within the processor and with external devices.

The key aspects of processor bus organization are:

1. Data Bus: The data bus is responsible for transferring data between the processor and other components, such as memory, input/output devices, and caches. It carries binary information in the form of data words or bytes. The width of the data bus determines the number of bits that can be transferred simultaneously. Common data bus widths are 8, 16, 32, or 64 bits.

2. Address Bus: The address bus carries the memory addresses that specify the locations where data is read from or written to. It enables the processor to select specific memory locations or input/output devices. The width of the address bus determines the maximum memory capacity that can be accessed. For example, a 16-bit address bus can access up to 64 KB (2^16) of memory.

3. Control Bus: The control bus carries control signals that coordinate and synchronize the operations of the processor and other components. It includes signals such as memory read and write control, interrupt requests, clock signals, and control signals for input/output operations. The control bus ensures proper timing and sequencing of operations within the processor.

4. Bus Width and Speed: The bus width refers to the number of parallel conductors in the bus, which determines the amount of data that can be transferred simultaneously. The bus speed, measured in MHz or GHz, indicates how fast data can be transferred on the bus. A wider bus and higher bus speed allow for faster data transfer between components.

5. Bus Architecture: The bus architecture can be organized in different ways based on the processor's design and requirements. Some common bus architectures include:

6. Bus Protocols: Bus protocols define the rules and procedures for data transfer and communication on the bus. They specify how data is encoded, how addresses are interpreted, and how control signals are managed. Common bus protocols include PCI (Peripheral Component Interconnect), USB (Universal Serial Bus), and SATA (Serial ATA).

The specific bus organization varies depending on the processor architecture and design choices. Different processor families and manufacturers may have their own unique bus organizations tailored to meet specific performance, compatibility, and power efficiency requirements.

1. System Bus: The system bus, also known as the front-side bus (FSB), is a high-speed bus that connects the processor to the main memory (RAM) and other major components in the computer system. It is responsible for transferring data, addresses, and control signals between the processor and other system components.

2. Address Bus: The address bus is a unidirectional bus that carries memory addresses. It is used by the processor to specify the memory location it wants to read from or write to. The width of the address bus determines the maximum memory capacity that can be addressed by the processor.

3. Data Bus: The data bus is a bidirectional bus that carries data between the processor and memory or other peripherals. It is used to transfer the actual data being read from or written to memory or other devices. The width of the data bus determines the maximum amount of data that can be transferred in a single bus cycle.

4. Control Bus: The control bus carries control signals that coordinate and control the operation of various components within the processor. It includes signals such as read and write control signals, interrupt signals, clock signals, and control signals for memory and I/O operations.

5. Internal Bus: The internal bus, also known as the local bus or backside bus, is an internal bus within the processor that connects the different units and components of the processor, such as the arithmetic logic unit (ALU), registers, and cache memory. It facilitates data transfer and communication within the processor itself.

6. Peripheral Buses: Apart from the internal processor buses, there are also buses dedicated to connecting the processor to external peripherals such as hard drives, graphics cards, USB devices, and network interfaces. Examples of peripheral buses include PCI (Peripheral Component Interconnect), PCIe (PCI Express), and USB (Universal Serial Bus).

Some common applications of processor bus organization:

1. Memory Access: The processor bus organization allows the processor to access different levels of memory hierarchies efficiently. It enables the transfer of data and instructions between the processor and memory modules, such as RAM and cache. The bus organization determines the data transfer rate, bus width, and protocols used for memory access, influencing the overall system performance.

2. I/O Device Communication: The processor bus organization facilitates communication between the processor and various input/output (I/O) devices. It enables the transfer of data between the processor and peripherals like keyboards, mice, displays, printers, and storage devices. The bus organization defines the protocols, addressing schemes, and data transfer rates required for I/O operations.

3. Interrupt Handling: Processor bus organization plays a crucial role in interrupt handling. Interrupts are signals generated by hardware or software events that require the processor's immediate attention. The bus organization allows interrupt signals to be efficiently communicated to the processor, enabling it to suspend the current task and handle the interrupt request promptly.

4. Cache Coherency: In systems with multiple processors or cores, maintaining cache coherency is essential to ensure data consistency. The processor bus organization provides mechanisms for cache coherency protocols such as MESI (Modified, Exclusive, Shared, Invalid) or MOESI (Modified, Owned, Exclusive, Shared, Invalid). These protocols enable the synchronization of data stored in different processor caches, ensuring that all processors have a consistent view of shared memory.

5. System Bus Arbitration: When multiple components in a computer system need to access the bus simultaneously, bus arbitration is required to manage access and prevent conflicts. The processor bus organization incorporates bus arbitration mechanisms to prioritize and schedule bus access requests from different components, ensuring fair and efficient utilization of the bus bandwidth.

6. System Configuration: Processor bus organization also assists in system configuration and initialization. It allows the processor to communicate with system configuration registers, which store information about hardware resources, system settings, and device initialization parameters. This enables the processor to configure and initialize various system components during the boot process.