Published by: Dikshya

Published date: 11 Jul 2023

The master-slave flip-flop is a type of sequential logic circuit that consists of two interconnected flip-flops: a master flip-flop and a slave flip-flop. It is designed to overcome certain limitations of basic flip-flops, such as race conditions and timing issues. Here are some key aspects and applications of the master-slave flip-flop:

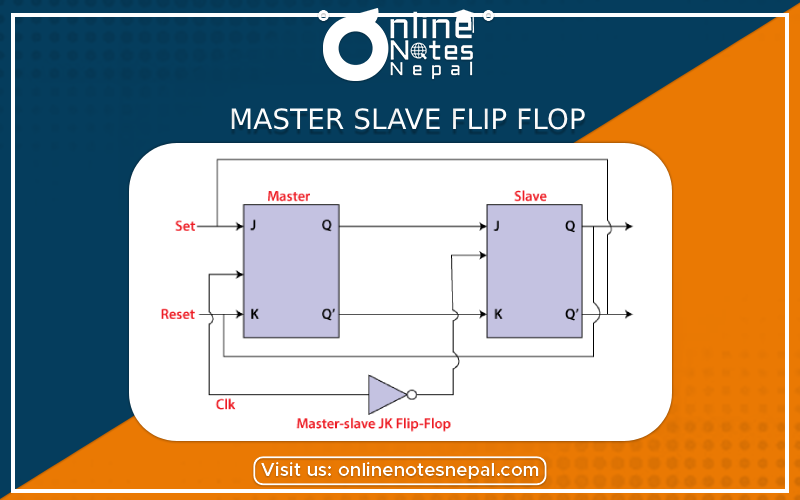

Structure: The master-slave flip-flop consists of two flip-flops connected in a cascade configuration. The output of the master flip-flop serves as the input for the slave flip-flop.

Timing and Synchronization: The master-slave configuration provides a mechanism for proper timing and synchronization of the input signal with respect to the clock signal. It eliminates race conditions and ensures reliable operation.

Clocking Scheme: The master flip-flop is enabled by the rising (positive-edge) or falling (negative-edge) edge of the clock signal, while the slave flip-flop is enabled by the opposite edge of the clock signal. This ensures that the input data is captured and transferred to the output only when the clock signal is stable.

Operation: The master flip-flop captures the input data during the active edge of the clock signal, and its output is then fed into the slave flip-flop. The slave flip-flop stores the data until the next clock edge, providing a stable output.

Data Transfer: The master-slave flip-flop allows for the controlled transfer of data from the master to the slave flip-flop, providing a delay between input and output. This delay is typically one clock cycle.

Timing Considerations: Master-slave flip-flops have specific timing requirements, such as setup time and hold time, to ensure reliable operation and prevent data corruption.

Applications: Master-slave flip-flops are widely used in applications where reliable and synchronized storage of data is required, such as in memory systems, control systems, state machines, and digital signal processing.

Edge-Triggered Operation: Master-slave flip-flops can be edge-triggered, meaning they respond to changes at the clock edge, or level-triggered, responding to the level of the clock signal.

High-Speed Circuits: Master-slave flip-flops are often employed in high-speed circuits where precise timing and reliable operation are critical, such as in microprocessors, high-speed communication systems, and digital signal processing applications.

Sequential Circuit Design: Master-slave flip-flops are a key component in designing complex sequential circuits that require synchronized data storage and controlled timing.