Published by: Nuru

Published date: 17 Jun 2021

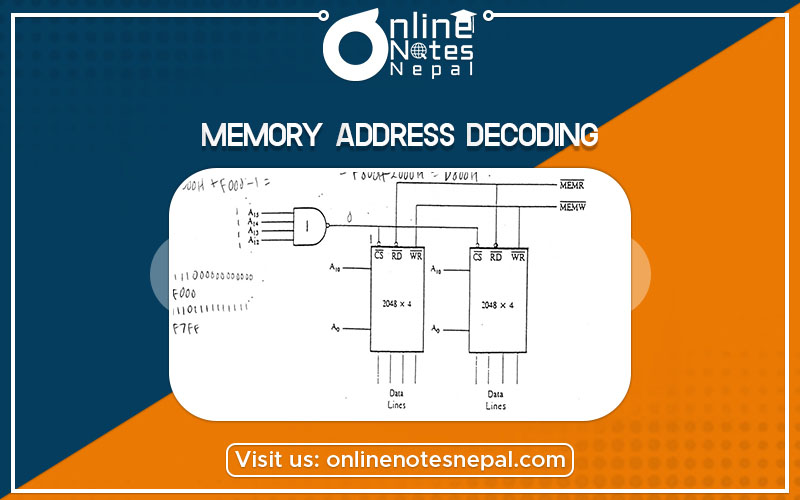

In Memory Address Decoding, the processor can usually address a memory space that is much larger than the memory space covered by an individual memory chip. In order to splice a memory device into the address space of the processor, decoding is necessary. It refers to the way a computer system decodes the addresses on the address bus to select memory locations in one or more memory or peripheral devices.

Depending upon the no. of address lines used to generate the chip select signal, the address decoding is classified as:

1. I/O mapped I/O

In this method, a device is identified with an 8-bit address and operated by I/O related functions IN and OUT for that IO/M =1. Since only an 8bit address is used, at most 256 bytes can be identified uniquely. Generally, low order address bits A0-A7 are used and upper bits A8-A15 are considered don’t care. Usually, I/O mapped I/O is used to map devices like 8255A, 8251A, etc.

2. Memory-mapped I/O

In this method, a device is identified with a 16-bit address and enabled memory-related functions such as STA, LDA for which IO/M =0, here chip select signal of each device is derived from 16-bit address lines thus total addressing capability is 64K bytes. Usually, memory-mapped I/O is used to map memories like RAM, ROM, etc.