Published by: Nuru

Published date: 17 Jun 2021

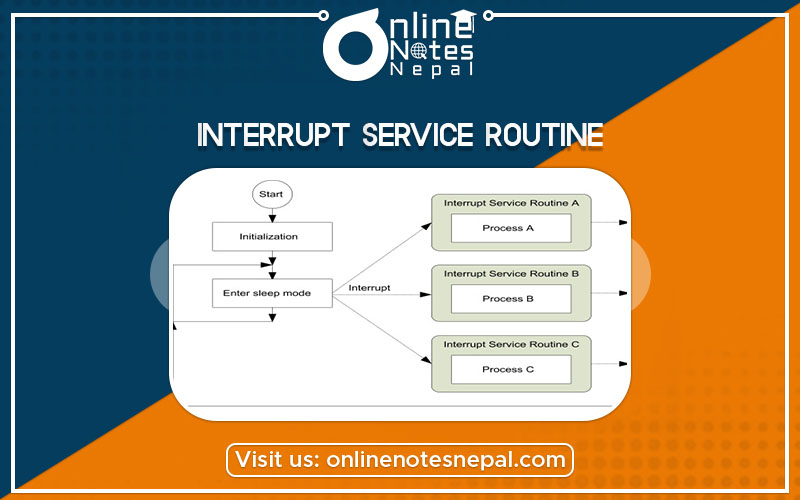

Interrupt service routine (ISR) is actually a call-back function (program) in the case of software or device driver (I/O device) in the case of hardware. When an interrupt is acknowledged by the processor, the routine or program which is running currently gets paused or interrupted, and the ISR program gets executed. An interrupt is a signal to the processor emitted by hardware or software indicating an event that needs immediate attention. Whenever an interrupt occurs, the controller completes the execution of the current instruction and starts the execution of an Interrupt Service Routine (ISR) or Interrupt Handler.

A small program or a routine that when executed, services the corresponding interrupting source is called an ISR.

TRAP

It is a non-maskable interrupt, having the highest priority among all interrupts. By default, it is enabled until it gets acknowledged. In case of failure, it executes as ISR and sends the data to backup memory. This interrupt transfers the control to location 0024H.

RST7.5

It is a maskable interrupt, having the second-highest priority among all interrupts. When this interrupt is executed, the processor saves the content of the PC register into the stack and branches to the 003CH address.

RST 6.5

It is a maskable interrupt, having the third-highest priority among all interrupts. When this interrupt is executed, the processor saves the content of the PC register into the stack and branches to the 0034H address.

RST 5.5

It is a maskable interrupt. When this interrupt is executed, the processor saves the content of the PC register into the stack and branches to the 002CH address.

INTR

It is a maskable interrupt, having the lowest priority among all interrupts. It can be disabled by resetting the microprocessor.

When the INTR signal goes high, the following events can occur −

ISR is responsible for doing the following things:

1. Saving the processor context

Because the ISR and main program use the same processor registers, it is the responsibility of the ISR to save the processor’s registers before beginning any processing of the interrupt. The processor context consists of the instruction pointer, registers, and any flags. Some processors perform this step automatically.

2. Acknowledging the interrupt

The ISR must clear the existing interrupt, which is done either in the peripheral that generated the interrupt, in the interrupt controller, or both.

3. Restoring the processor context

After interrupt processing, in order to resume the main program, the values that were saved prior to the ISR execution must be restored. Some processors perform this step automatically.